Unexcepted decoder output

Posted: Sat Jul 12, 2014 4:22 am

Hello there.

I have create a decoder, but I get an unexcepted output.

They excepted outputs are:

p should be the previouse output.

But for the test, i have deactivated 0b10101xyz (q = 0b00), 0b01110xyz (q=0b11) and p get constantly 1.

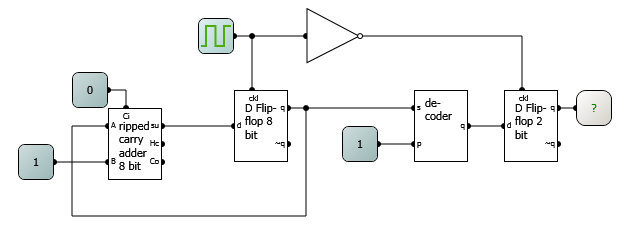

On the rising edge of the clock, the left D flipflop update the value from the ripped carry adder to the decoder (and the adders input). On the falling edge, the value from the decoder will update to the probe.

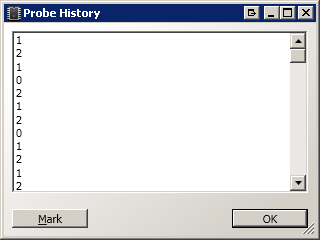

But sometimes I get on the probe the unexcepted value 0 for a short time.

Do anyone see whats there wrong? Because the decoder controll a multiplexer, I get in my main circuit a wrong result.

Thank you

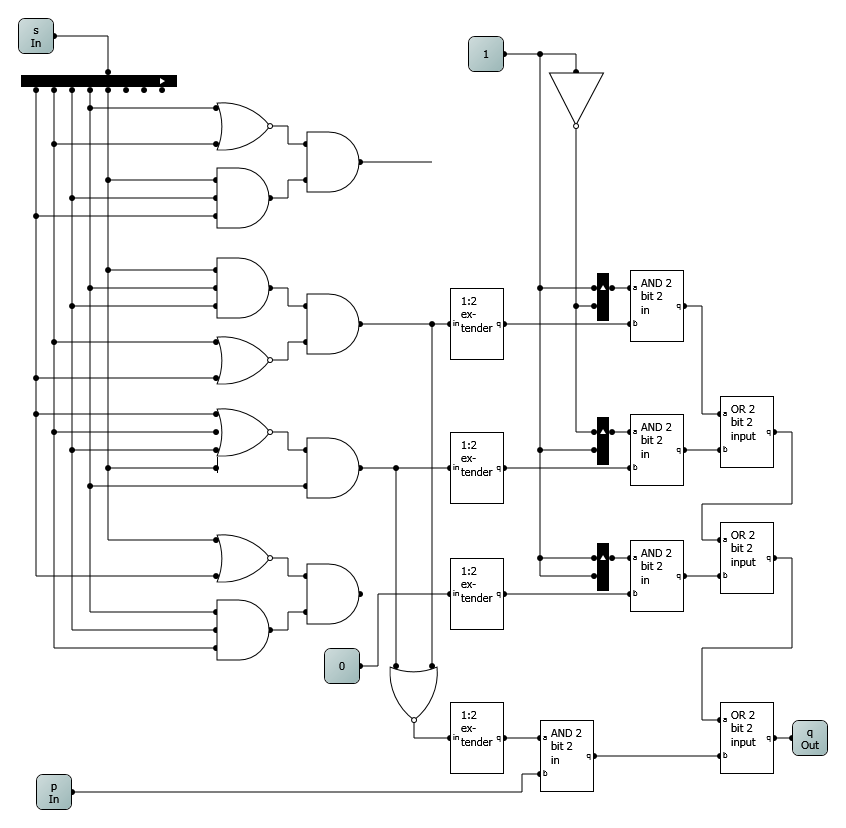

(The "Extender" copy the incoming bit to all outgoing bits.)

I have create a decoder, but I get an unexcepted output.

They excepted outputs are:

Code: Select all

s q

0b10101xyz 0b00

0b00111xyz 0b01

0b00010xyz 0b10

0b01110xyz 0b11

All others p

But for the test, i have deactivated 0b10101xyz (q = 0b00), 0b01110xyz (q=0b11) and p get constantly 1.

On the rising edge of the clock, the left D flipflop update the value from the ripped carry adder to the decoder (and the adders input). On the falling edge, the value from the decoder will update to the probe.

But sometimes I get on the probe the unexcepted value 0 for a short time.

Do anyone see whats there wrong? Because the decoder controll a multiplexer, I get in my main circuit a wrong result.

Thank you

(The "Extender" copy the incoming bit to all outgoing bits.)